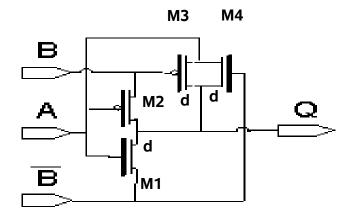

(1) Determine the function table of the following circuit (note: all drains connect to Q):

|   |   | M1: nmos On=Vg>Vs |    |        | M2: | pmo | s On=Vg | g <vs< th=""><th><i>M3</i>:</th><th>pmo</th><th>s On=Vg</th><th>g<vs< th=""><th>M4</th><th>: nmo</th><th>os on=Vg</th><th>&gt;Vs</th><th>Q</th></vs<></th></vs<> | <i>M3</i> : | pmo | s On=Vg | g <vs< th=""><th>M4</th><th>: nmo</th><th>os on=Vg</th><th>&gt;Vs</th><th>Q</th></vs<> | M4 | : nmo | os on=Vg | >Vs    | Q  |   |

|---|---|-------------------|----|--------|-----|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----|---------|----------------------------------------------------------------------------------------|----|-------|----------|--------|----|---|

|   |   | Vg                | Vs | on/off | Vd  | Vg  | Vs      | on/off                                                                                                                                                           | Vd          | Vg  | Vs      | on/off                                                                                 | Vd | Vg    | Vs       | on/off | Vd |   |

| Α | В | Α                 | ~B |        |     | Α   | В       |                                                                                                                                                                  |             | В   | Α       |                                                                                        |    | ~B    | Α        |        |    |   |

| 0 | 0 | 0                 | 1  | off    | Ζ   | 0   | 0       | off                                                                                                                                                              | Ζ           | 0   | 0       | off                                                                                    | Ζ  | 1     | 0        | on     | 0  | 0 |

| 0 | 1 | 0                 | 0  | off    | Ζ   | 0   | 1       | on                                                                                                                                                               | 1           | 1   | 0       | off                                                                                    | Ζ  | 0     | 0        | off    | Ζ  | 1 |

| 1 | 0 | 1                 | 1  | off    | Ζ   | 1   | 0       | off                                                                                                                                                              | Ζ           | 0   | 1       | on                                                                                     | 1  | 1     | 1        | off    | Ζ  | 1 |

| 1 | 1 | 1                 | 0  | on     | 0   | 1   | 1       | off                                                                                                                                                              | Ζ           | 1   | 1       | off                                                                                    | Z  | 0     | 1        | off    | Ζ  | 0 |

NMOS: if Vg>Vs then ON and Drain is connected to Source; else OFF; PMOS: if Vg<Vs then ON and Drain is connected to Source; else OFF;

Q = M1(Vd) + M2(Vd) + M3(Vd) + M4(Vd);

```

(2) Write the SPICE .subchk for the circuit in problem 1.

(Given, A=1, B=2, BNOT=3, Q=4, VDD=5, PCH for PMOS, NCH for NMOS, W=5U, L=5U).

```

.SUBCKT XOR1X 1 2 3 4 5

\*

```

* .SUBCKT XOR1X A=1 B=2 BNOT=3 Q=4 VDD=5

```

| *Mname | DRAIN | GATE | SOURCE | SUBSTRATE | MODEL | WIDTH   | LENGTH  |

|--------|-------|------|--------|-----------|-------|---------|---------|

| *      | NODE  | NODE | NODE   | NODE      | NAME  | MICRONS | MICRONS |

| *      |       |      |        |           |       |         |         |

| M1     | 4     | 1    | 3      | 0         | NCH   | W=5U    | L=2U    |

| M2     | 4     | 1    | 2      | 5         | PCH   | W=5U    | L=2U    |

| M3     | 4     | 2    | 1      | 5         | PCH   | W=5U    | L=2U    |

| M4     | 4     | 3    | 1      | 0         | NCH   | W=5U    | L=2U    |

| .ENDS  | XOR1X |      |        |           |       |         |         |

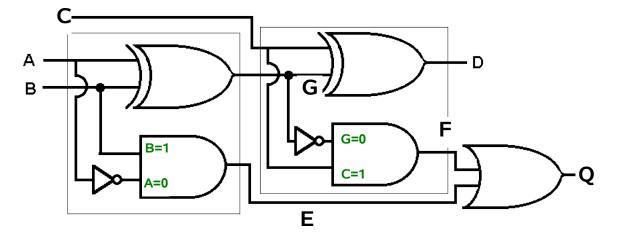

(3) Give the logical expression in VHDL notation for the following logic circuit:

$D \leq (C XOR (A XOR B));$

E <= NOT(A) AND B; F<=C AND NOT(G); G<=A XOR B; Q<=F OR E

$Q \leq (C \text{ AND NOT}(A \text{ XOR B})) \text{ OR (NOT}(A) \text{ AND B});$

(4) Fill in the truth table: (blanks also mean false or zero).

For ANDs first fill in the trues (why only one case). For ORs fill in the falses first.

E = true only when A=0 and B=1;

G = true only when A or B is odd number of one bits.

F = true only when C=1 and G=0;

D=is it odd number of bits?;

Q = false only F=0 and E=0; then fill blanks with 1's;

| A | B | С | E       | F | G | D | Q |

|---|---|---|---------|---|---|---|---|

| 0 | 0 | 0 |         |   |   |   | 0 |

| 0 | 0 | 1 |         | 1 |   | 1 | 1 |

| 0 | 1 | 0 | 1       |   | 1 | 1 | 1 |

| 0 | 1 | 1 | 1       |   | 1 |   | 1 |

| 1 | 0 | 0 |         |   | 1 | 1 | 0 |

| 1 | 0 | 1 |         |   | 1 |   | 0 |

| 1 | 1 | 0 |         |   |   |   | 0 |

| 1 | 1 | 1 | <u></u> | 1 |   | 1 | 1 |

(5) Redraw problem 3 using only NOR Gates for output Q only.

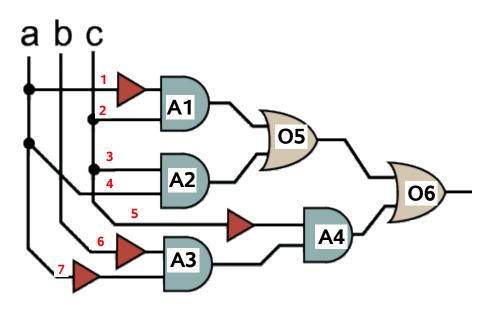

(6) Given that NOT has delay of 10ns, NAND 20ns, and NOR 40ns for the following circuit what is the minimum and maximum delay and show work (note: circuit contains BUFFERs, ANDs, and ORs):

(a) Delay for a BUFFER is 10ns+10ns = 20ns

- (b) Delay for AND using only NAND and NOT \_\_\_\_\_20ns+10ns=30ns\_\_\_\_\_

(c) Delay for OR using only NOR and NOT is \_\_\_\_\_40ns+10ns=50ns\_\_\_\_\_

- (d) What is the minimum delay = 100 ns and through what gates: BUFFER+A4+O6 . . . . . . .

- (e) What is the maximum delay = 150ns and through what gates: BUFFER+A1+O5+O6

parh 1: (input a): BUFFER+A1+O5+O6 = 20 + 30 + 50 + 50 = 150 maximum path 2: (input c): A1 + O5 + O6 = 30+50+50 = 130 path 3: (input c): A2 + O5 + O6 = 130path 4: (input a): A2 + O5 + O6 = 130path 5: (input c): BUFFER+A4+O6=20+30+50=100 minimum path 6: (input b): BUFFER+A3+A4+O6=20+30+30+50=130 path 7: (input a): BUFFER+A3+A4+O6=130

(7) Design a logic expression for a coke machine which releases one coke can (Q) whenever the minimum amount of 20 cents is entered. The coin box outputs 3 signals when a 5 cent coin (A), 10 cent coin (B), and 25 cent coin (C) in parallel is received. The coin box will only accept at most one coin of each type. Please show work.

Q <= (NOT(A) AND NOT(B) AND C) OR (NOT(A) AND B AND C) OR (A AND NOT(B) AND C) OR (A AND B AND C);

| A  | B   | С   | Total       | Q | ANDs        |

|----|-----|-----|-------------|---|-------------|

| 5¢ | 10¢ | 25¢ |             |   |             |

| 0  | 0   | 0   | 0¢          |   |             |

| 0  | 0   | 1   | 25¢         | 1 | ~A & ~B & C |

| 0  | 1   | 0   | 10¢         |   |             |

| 0  | 1   | 1   | 35¢         | 1 | ~A & B & C  |

| 1  | 0   | 0   | 5¢          |   |             |

| 1  | 0   | 1   | <b>30</b> ¢ | 1 | A & ~B & C  |

| 1  | 1   | 0   | 15¢         |   |             |

| 1  | 1   | 1   | <b>40</b> ¢ | 1 | A & B & C   |